최근 삼성전자가 세계 최초로 3나노 공정으로 반도체 양산을 시작하면서 트랜지스터(transistor) 구조에 대한 관심이 커졌다. 반도체 소자의 기본 구조는 트랜지스터다. 전류를 연결하거나 끊는 디지털 스위치 역할을 한다. 반도체 칩 하나에 트랜지스터가 최대 100억개 들어있다.

트랜지스터 크기를 줄이면 정보 처리 속도가 빨라지고 전력 소모도 줄어든다. 그래서 원자 수준에 가까운 나노미터(nm·10억분의 1m) 크기까지 줄이려 하고 있다. 반도체 원재료인 웨이퍼 원판에 머리카락 굵기의 10만분의 1 선폭(線幅)으로 미세회로를 그려 넣겠다는 것이다. 그동안 반도체 최신 공정은 4나노미터였는데 이번에 삼성전자가 3나노미터 공정 시대를 열었다. 대만 TSMC와 미국 인텔도 사활을 걸고 경쟁하고 있다.

◆전류 통로 확대해 속도 향상

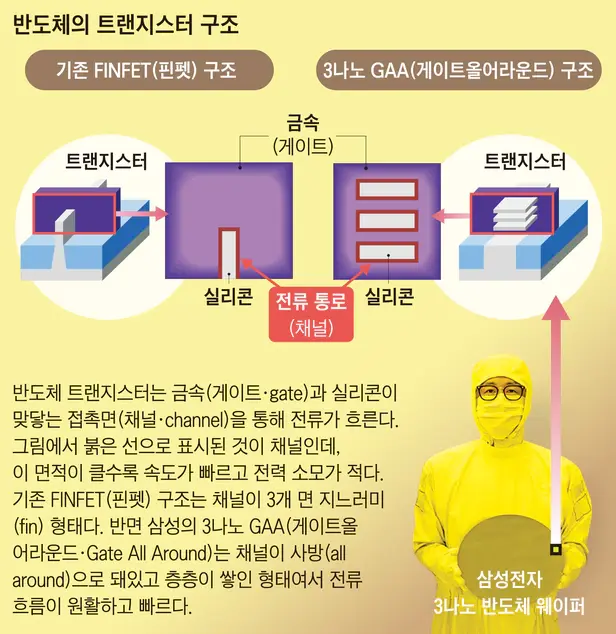

반도체 트랜지스터는 게이트(gate)로 불리는 금속과, 실리콘 등으로 이뤄져 있다. 실리콘과 금속(게이트)이 맞닿은 ‘전류 통로(채널)’ 면적이 넓을수록 연산 속도가 빠르고 전력 소모가 적다. 그런데 나노미터 크기로 줄어들면 통로가 너무 좁아져 전류를 충분히 흘리는 데 제한이 있다. 이렇게 되면 계산 시간이 지체되고 저항이 증가한다.

이를 해결하기 위해선 실리콘과 금속이 맞닿는 전류 통로 면적을 확대해야 한다. 그래서 개발한 구조가 지느러미 모양의 핀펫(FINFET) 구조다. TSMC가 세계 파운드리 시장을 장악하면서 사용한 구조다. 그런데 이 구조도 전류의 손실, 발열 등 문제를 갖고 있다.

이 한계를 극복하고자 고안한 새로운 구조가 바로 3나노미터 GAA(게이트올어라운드·Gate All Around)다. 이는 삼성전자가 TSMC를 넘어서기 위한 비장의 기술이다. GAA 구조에서는 전류 통로(채널) 표면적을 더욱 넓히기 위해 사방을 둘러싸는 형태로 만들고, 여러 개 다층구조로 쌓았다. 실리콘과 금속이 맞닿는 접촉면을 대폭 늘려 전류 흐름을 더욱 원활하게 만든 것이다.

◆로마 다층 다리 구조와 유사

로마제국에서는 머나먼 수원지에서 도시나 마을의 공중목욕탕, 공중화장실, 분수, 그리고 사유지에 수돗물을 공급하기 위해 다층 수도교(水道橋)를 건설했다. 위층으로는 물을 흘리고 아래층으로는 사람들이 다니는 다리를 만든 것이다. 현재 남부 프랑스에 있는 퐁뒤가르(Pont du Gard) 다목적 아치교가 좋은 예이다. 여기서 GAA 다층 구조에 대한 영감을 얻는다. 이처럼 GAA 구조는 원자 수준의 크기로 지하 통로, 지면 통로, 고층 통로로 이루어진 다층 구조물이다.

|

(요약) 1. 3 나노 반도체는 원자수준 (양자)의 예술이다.- 전자현미경으로만 관찰된다. 2. 3나노 반도체는 전류의 흐름을 종전보자 다층화하여 종전보다 많은 전류가 흐르고 흐르는 속도가 빨라진 구조이다. 3. 반도체 트란지스터는 전류 흐름을 이었다 귾었다 하는 디디털 스윗지 역할을 하고 1개 반도체 칩에 최대 100억개 트란지스터가 들어 있다. 4. 반도체 트란지스터는 금속(게이트)과 실리콘 판이 맞닿는 접촉면 체널을 통해 전류가 흐른다. 이 접촉면을 늘려가는 기술이 반도체 집적도를 계속 높인다. (조선일보 2022.8.3 보도 오피니언 란) |

'컴퓨터, 공학 들' 카테고리의 다른 글

| 우주 과학 글 (0) | 2022.08.09 |

|---|---|

| 다누리 발사 보도 (0) | 2022.08.06 |

| 허준이 교수 그리고 러시아 코발렙스키야 수학과 시 (0) | 2022.08.03 |

| 세계 최초로 삼성의 3나노 반도체 생산 시작 (0) | 2022.07.04 |

| 컴 고치는 만능 버튼 (0) | 2022.03.08 |